Assisting designers in maximizing the full benefits that incremental compilation provides, Quartus II software version 8.0 features a new design partition planner. Quartus II software's incremental compilation feature is claimed to offer users a second-to-none productivity advantage, capable of delivering up to a 70 percent compile time reduction compared to a standard compilation. Designs leveraging multiprocessor-based servers will obtain an even higher compile time advantage –an additional 20 percent reduction on average– using what Altera say is the industry's only vendor-supplied FPGA design software with multiprocessor support. Users of Linux platforms will see average compile times decrease by more than 30 percent.

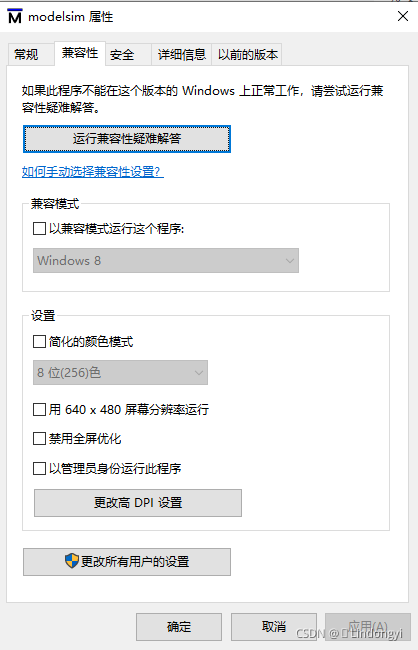

Customers using the 8.0 release to design Altera's 65-nm Stratix III FPGAs on Windows platforms will see compile times reduced by up to 50 percent, with an average reduction of 22 percent, when compared to version 7.2. Over the past five years, Quartus II software is said to have consistently delivered the industry's fastest compile times for high-end FPGAs, averaging a 20 percent reduction annually. With new productivity features and support for the industry's most advanced FPGAs, the folks at Altera say that this version 8.0 release reinforces their commitment to deliver the highest level of performance and productivity to FPGA designers. What is of interest is that this version of the Quartus II software is claimed to deliver, on average, a full two-speed grade advantage and 3X faster compile times for high-end FPGAs when compared to the nearest competitor's latest offering (this is “fighting talk” if ever I heard it). With ModelSim Altera Edition I can use this test bench without any problems.It probably comes as no surprise to hear that the folks at Altera have announced that their Quartus II software version 8.0 supports their newly announced 40nm Stratix IV FPGAs and HardCopy IV ASICs. (Line 43 is the statement " wait for 500ns ") Use altera.altera_primitives_components.all Īnd I got again and again the error message:Įrror (10533): vhdl wait statement error at testbench_1.vhd(43): wait statement must contain condition clause with until keyword. I tried the following test bench with Quartus 9.1 SP2 : It is really a pity, that this feature is not implemented.Īpropos the test benches. Test benches are surely a good workaround and surely the most certain way to simulate a design, but sometimes one needs an opportunity for quick test without to have to write a new test bench.

0 kommentar(er)

0 kommentar(er)